美国豪威公司的微型影像模组封装技术(CameraCubeChip)和硅基液晶投影显示芯片(LCOS)广泛应用于消费电子和工业应用领域。其CameraCubeChip产品凭借专有的堆叠技术完成晶圆级光学器件与硅片的结合,具有强大的市场竞争力。

随着人们对高质量影像的追求,内部包括逻辑晶圆和像素晶圆的堆叠式CMOS图像传感器逐步进入市场。与传统CMOS传感器相比,堆叠式的传感器具有更小的芯片结构和更快的处理速度,并应用了TSV(硅通孔)技术,实现芯片与芯片之间、晶圆和晶圆之间的垂直导通与互连,使其在三维方向堆叠密度更大。然而现有技术中TSV嵌套孔在横向上占用了较大面积,限制了像素晶圆上的像素单元数量,进而限制了堆叠式CMOS图像传感器向更高像素的发展。

为此,豪威科技公司于2018年2月6日提出一项名为“堆叠式CMOS图像传感器及其制作方法”的发明专利(申请号:201811418938.X),申请人为豪威科技(上海)有限公司。

此项专利核心在于提供一种堆叠式CMOS图像传感器及制作方法,减小了逻辑晶圆和像素晶圆金属层互连孔的横向尺寸,同时简化了堆叠式CMOS图像传感器的制作工艺。

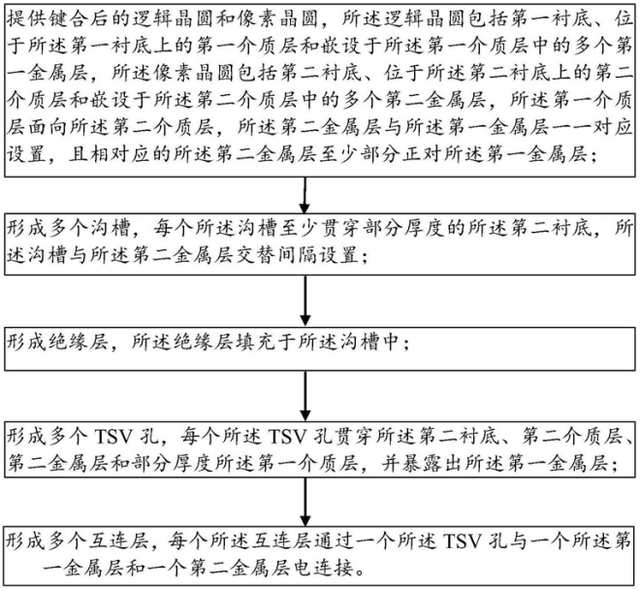

图1 堆叠式CMOS图像传感器制作方法

该专利提出的堆叠式CMOS图像传感器制作方法如图1,首先提供键合后的逻辑晶圆和像素晶圆,其中逻辑晶圆和像素晶圆分别包括第一衬底/第二衬底、第一介质层/第二介质层以及多个第一金属层/第二金属层,两种介质层和金属层一一对应。其次要形成多个沟槽,并与第二金属层交替间隔设置,形成绝缘层并填充于沟槽中。然后形成多个TSV孔,贯穿第二衬底、第二介质层、第二金属层和部分厚度的第一介质层,并暴露出第一金属层。最后形成多个互连层,每个互连层通过TSV孔与第一金属层和第二金属层电连接。

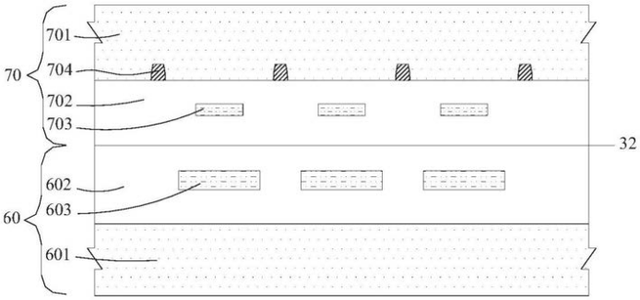

图2 键合后的逻辑晶圆和像素晶圆示意图

图2提供了键合后的逻辑晶圆60和像素晶圆70,第一介质层602面向第二介质层702键合,形成键合界面32,第二金属层703与第一金属层603在空间上正对,并呈现阵列分布,且第二金属层的投影完全落入第一金属层中。第二衬底靠近第二介质层的一侧间隔分布多个浅槽隔离单元704,用于隔离相邻两侧的第二衬底。

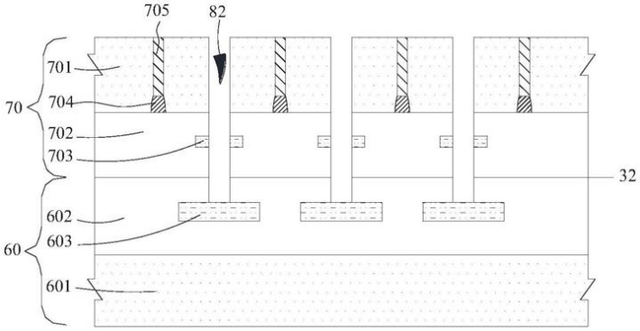

图3 TSV孔示意图

图3表示使用干法刻蚀形成的TSV孔82,需要贯穿第二衬底、第二介质层、第二金属层703和部分厚度的第一介质层,并在表面显现出第一金属层。同时相邻的TSV孔82之间需通过绝缘层705隔离,以形成相互独立的单元,防止其他TSV孔中的互连层对周围单元造成影响。

以上就是豪威科技此项发明的所有内容,与现有技术相比,改良的技术版本通过减小TSV孔的横向间距,使逻辑晶圆和像素晶圆上可容纳更多的TSV孔,实现更多像素单元,大大提升了传感器的成像效果。